更高的數據速率和更復雜的功能正在增加超大規模數據中心、人工智能和網絡應用程序的SoC大小。當SoC尺寸接近最小分劃線尺寸時,設計者被迫將SoC拆分成更小的晶粒,以獲得更高的生產良率并降低總成本。此類soc中的Die-to-Die互連,要求不能影響整個系統的性能,并且要低延遲、高能效和高吞吐量。這些要求推動了對高吞吐量晶粒間(Die-to-Die)的物理需求。

超大規模數據中心、人工智能(AI)和網絡應用的SoC設計人員面臨著大數據時代以來的諸多挑戰。由于工作負載需求和更快地移動數據的需要,此類soc已經變得更加復雜,具有更高級的功能,并達到了最大的網線大小。因此,設計人員將soc劃分到多芯片模塊(MCM)封裝中的較小模塊中。為了支持具有高數據速率的晶粒連接,這些分散的芯片需要超短的連接。除了帶寬之外,晶粒間的連接必須確保可靠,并且具有極低的延遲和電源效率。本文描述了幾個不同的晶粒間連接用例,以及在搜索用于晶粒間連接的高速PHY IP時需要考慮的基本事項。

在MCM封裝中出現了用于模塊間連接的新用例,其中包括:

高性能計算和接近最大網線大小的服務器soc

超過最大網線尺寸的以太網交換機和網絡soc

基于分布式SRAM的人工智能(AI) soc來擴展復雜的算法

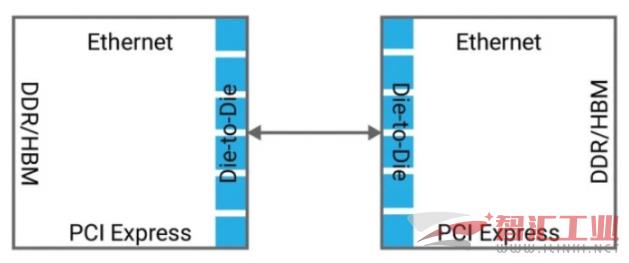

高性能計算和服務器SoC的規模越來越大,可達到550mm2到800 mm2,從而減少了SoC的產量,但增加了每個芯片的成本。優化SoC良率的一個更好的方法是將SoC分成兩個或多個等價的同質模組,如圖所示,并使用一個晶粒間 PHY IP連接這些模組。在這樣的用例中,最關鍵要保證極低的延遲和零誤碼率,因為較小的晶粒必須描述和表現為單個晶粒。

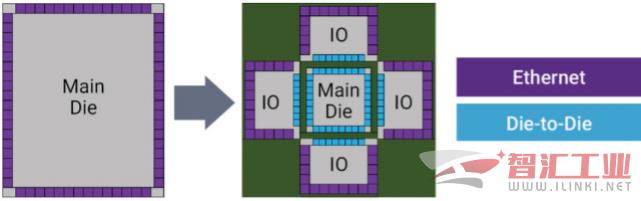

以太網交換機SoC是數據中心的核心,它必須以更快的速度將數據從12 Tbps移動到25 Tbps,而這需要100G SerDes接口的256條通道,這不太可能在800 mm2的網線區域內容納SoC。為了克服這一挑戰,設計人員將SoC分解為一個配置,其中核心晶粒被I/O 晶粒包圍,如下圖所示。然后使用晶粒間的收發器將晶圓連接到I/O模上。

在這個用例中,只有當晶粒間收發機的帶寬密度遠遠優于I/O模中的長范圍并行轉換器SerDes時,晶粒切割才有效。因此,關鍵參數是每毫米的晶粒邊帶寬(Die-edge bandwidth)密度。

晶粒間連接的以太網交換機SoC的示例

所有這些用例中,用于Die之間連接的理想高速PHY可以簡化MCM封裝要求。由于每條通道的高吞吐量可達112 Gbps,因此相對有限的通道數可以實現非常高的總吞吐量。在這種情況下,在這種情況下,封裝跟蹤間距和堆棧可以是保守的(L/S為10u/10u最常見)。在這些用例中,還可以使用傳統低成本、基于有機基質的封裝。

高速物理層IP對Die之間連接的要求

光互連論壇(OIF)正在定義用于數據速率高達112 Gbps的超短連接(USR)和超短連接(XSR)傳輸的電I/O標準。這些規范定義了Die之間的鏈接和Die之間的光學引擎,它與SoC位于同一封裝內,這大大降低了功耗和復雜性,并具有非常高的吞吐量密度。

SoC設計人員在研究MCM中用于芯片間連接的高速PHY IP解決方案時,必須考慮幾個基本特性:數據吞吐量或帶寬、能源效率(以皮焦耳/比特為單位)、延遲(以納秒為單位)、最大鏈路長度(以毫米為單位)和誤碼率。

數據吞吐量或帶寬

為了實現與其他收發器的互操作性,Die之間的IP必須確保符合USR和XSR鏈路相關的OIF電氣規范。支持脈沖幅度調制(PAM-4)和不歸零(NRZ)信令對于滿足這兩種鏈路要求并實現每路最大112 Gbps的帶寬至關重要。這種信令會導致非常高的帶寬效率,這是一個關鍵的要求,因為在MCM的晶粒之間傳輸的數據量非常大。數據移動速度通常在每秒兆位級別,這限制了分配給USR和XSR鏈路的芯片邊緣的大小。

然而,同樣重要的是支持廣泛的數據速率。通常,如果數據速率與內部結構中使用的數據或者支持Die之間協議所需的所有數據速率一致,那么實現Die之間的鏈接是最好的。例如,即使在32 Gbps這樣的高速下,PCIe在協議初始化時也必須支持將數據速率降至2.5 Gbps。

鏈接

在Die之間中,大量的數據必須通過晶粒間隙的短數據路徑。為了保證晶粒放置在封裝基板上的最大靈活性,PHY IP必須支持TX和RX之間的距離要達到50毫米。

能源效率

能源效率成為一個重要的因素,特別是在SoC功能被分割成多個同類晶粒的情況下。在這種情況下,設計人員會尋找在不影響SoC總功率預算的情況下,在Die之間傳輸大量數據的方法。理想的Die之間IP提供的能量效率比每比特(1pJ/bit)或1mW/Gbps更好。

延遲和誤碼率

為了使Die之間的連接“透明”,延遲必須非常低,同時必須優化誤碼率(BER)。對于簡化的體系結構,Die之間PHY IP本身要實現超低延遲,BER優于10e-15。根據鏈路范圍的不同,互連可能需要使用前向糾錯(FEC)機制來保護,以實現如此低的誤碼率。FEC延遲影響著解決方案的總體延遲。

宏觀布局

除了這些與性能相關的參數外,PHY IP還必須支持芯片的所有側面的布置,以實現芯片以及MCM的有效布局。通過對宏的優化,可以實現低耦合的高效晶粒間路由,優化晶粒和MCM區域,最終提高功率效率。

在選擇一個Die之間的IP時,還有許多其他因素要考慮,包括可測試特性,這保障在封裝之前對晶粒進行生產測試,但以上是最基本的。

(審核編輯: 智匯婷婷)

分享