EDA技術就是以計算機為工具.設計者在EDA軟件平臺上,用相對應得電路結構或硬件描述語言VHDL完成設計文件,然后由計算機自動地完成邏輯編譯、化簡、分割、綜合、優化、布局、布線和仿真,直至對于特定目標芯片的適配編譯、邏輯映射和編程下載等工作。EDA技術的出現,極大地提高了電路設計的效率和可操作性,減輕了設計者的勞動強度。利用EDA工具,電子設計師可以從概念、算法、協議等開始設計電子系統,大量工作可以通過計算機完成,并可以將電子產品從電路設計、性能分析到設計出IC版圖或PCB版圖的整個過程的計算機上自動處理完成,因此,EDA技術在電路設計的具有非常重要的應用。

電路系統一般包括輸入電路、控制轉換電路、輸出電路和電源電路等部分。任何復雜的電子電路系統都可以逐步劃分成不同層次、相對獨立的子系統。通過對子系統的輸入輸出關系、時序等的分析,最后可以選用合適的電子電路器件來實現,將各子系統組合起來.便完成了整個大系統的設計。電子電路系統設計的一般方法與步驟可分為:

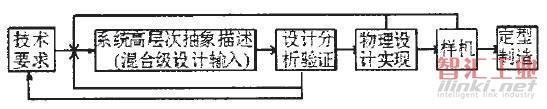

圖1 電子電路系統設計的一般方法與步驟

一、消化課題

必須充分了解設計要求,明確被設計系統的全部功能、要求及技術指標。熟悉被處理信號與被控制轉換對象的各種參數與特點。設計的基本流程如下圖:

二、確定總體設計方案

根據系統總體功能畫出系統的原理框圖,將系統分解。確定連接不同方框間各種信號的相互關系與時序關系。方框圖應能簡潔、清晰地表示設計方案的原理。

三、繪制單元電路并對單元電路并對單元電路進行仿真

選擇合適的電路器件,用電子仿真軟件繪出個單元的電路圖。然后利用電子軟件中的電路仿真功能對設計的電路進行仿真測試,從而確定設計的電路是否正確。

若電路中采用了TTL、COMS、運放、分立元件等多種器件時,如果采用不同的電源供電,則要注意不同電路之間電平的正確轉換,并應繪制出電平轉換電路。

在仿真電路時,可以選擇不同的仿真軟件,目前電子行業有很多不同的仿真軟件,有SPICE、Multisim、Proteus等很多種,本人從事電子教學設計多年,總結了一些方法,基礎電路仿真主要使用使用Multisim軟件,控制電路仿真使用Proteus,通信電路仿真使用MATLAB等。

仿真電路軟件給設計者帶來了很大的方便,設計好的電路圖通過仿真軟件進行實時模擬,模擬出實際功能,然后通過其分析改進,從而實現電路的優化設計。不僅節約了時間,對硬件缺乏的設計者來說節省了一筆開支。近年來,各高校都引入了仿真軟件教學課程,使大學生在電路設計時應用EDA工具,輔助電路設計,極大的提高了學生的動手能力和創新思維能力,同時也為高校硬件資源的投資建設節約了開支。

四、分析電路

設計的電路可能不存在任何問題,但組合起來后系統可能不能正常工作,因此,充分分析各單元電路,特別是對控制信號要從輸入輸出關系、正負極性、時序等幾個方面進行深入的考慮,確保不存在沖突。在深入分析的基礎上通過對原設計電路的不斷修改,從而獲得最佳設計方案。

五、完成整體設計

在各單元電路完成的基礎上,再用電子仿真軟件對整個電路進行仿真,驗證設計。根據設計要求來設計出一個比較理想的電子電路系統須經常訓練,反復實踐才能熟練。由于電子仿真元器件模型的典型化及真實元器件參數的離散性、電路連線或印制板形成的分布參數、電子裝配工藝等方面的原因,工程上,設計完成的電路必須經過實體安裝、調整、測試驗證后才能投產,形成產品。

對以正確分析電路原理圖后,進行硬件電路的制作,首先就是設計硬件電路原理圖,可以通過幾種方法實現,Proteus、Protel、Altium Designer、Mentor等可以實現原理圖的繪制及PCB板圖的設計。目前對于高職院校電子技術實驗教學,使用較多的是Protel、AltiumDesigner軟件。設計完成原理圖SCH文件后可以進行電路電氣性能正確性檢查,仿真軟件可以自動檢測錯誤連接方式,提示設計者改正,最后完成正確的電路原理圖設計。接著實現PCB板設計。盡管現在的EDA工具很強大,但隨著PCB尺寸要求越來越小,器件密度越來越高,極其苛刻的布線規則,這些都使得PCB設計的難度并不小。如何實現PCB高的布通率以及縮短設計時間呢?本人以為從信號完整性設計、工藝及結構設計、熱設計三方面進行處理。合理的PCB圖設計完成后交付電路板加工廠加工。

以上五個步驟可以實現了一個具有原始設計的電路板,再通過元件焊接、調試、再反復修改電路設計、再調試,直到完成一個合理的設計作品。如設計的為產品,則需要進行相關測試,完成相關部門的工程驗收,才能成為合格產品。

六、結語

EDA代表了當今電子設計技術的最新發展方向,利用EDA工具,電子設計師可以從概念、算法、協議等開始設計電子系統,大量工作可以通過計算機完成,并可以將電子產品從電路設計、性能分析到設計出IC版圖或PCB版圖的整個過程在計算機上自動處理完成。設計者采用的設計方法是一種高層次的”自頂向下”的全新設計方法,這種設汁方法首先從系統設計入手,在頂層進行功能方框圖的劃分和結構設計。在方框圖一級進行仿真、糾錯.并用硬件描述語言對高層次的系統行為進行描述,在系統一級進行駛證。然后,用綜合優化工具生成具體門電路的網絡表,其對應的物理實現級可以是印刷電路板或專用集成電路(ASIC)。設計者的工作僅限于利用軟件的方式,即利用硬件描述語言和EDA軟件來完成對系統硬件功能的實現。由于設計的主要仿真和調試過程是在高層次上完成的,這既有利于早期發現結構設計上的錯誤,避免設計工作的浪費,又減少了邏輯功能仿真的工作量,提高了設計的一次性成功率。

(審核編輯: 智匯胡妮)

分享