許多市場領域(包括視頻廣播、軍事、醫學影像、基站)都得益于使用高密度FIFO器件方案的使用,其具有可編程的特點。并且比SDRAM + FPGA的體系結構可以顯著節省成本和改進視頻質量,使用系統級編程,可以使高密度FIFO設計更簡單,成本更低。

在這篇文章中,我們將首先介紹幾個視頻應用,了解其數據路徑及需要處理的數據性質。下一步,我們將盡力估計在視頻處理通道中操作數據的復雜性。然后會介紹可編程高密度FIFO和其能力,以及它如何能更有效率的替代當前傳統的使用SDRAM和FPGA實現幀緩存的方案。

視頻應用概述:

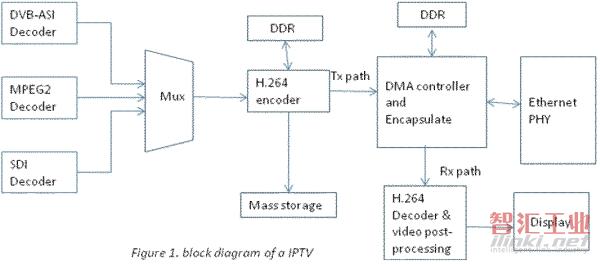

圖1顯示了IPTV的系統框圖。輸入傳輸流可以是任何編碼形式如DVB -ASI,MPEG2或SDI,他們通過用多格式解碼器(multi-format CODEC)傳輸,轉換成(即解碼或重解碼)成H.264傳輸流。經編碼的傳輸流用通道信息封裝并通過以太網發送。在接收路徑,到來的傳輸流在顯示之前要進行解碼和后處理,例如降噪、顏色增強,縮放,去隔行等。

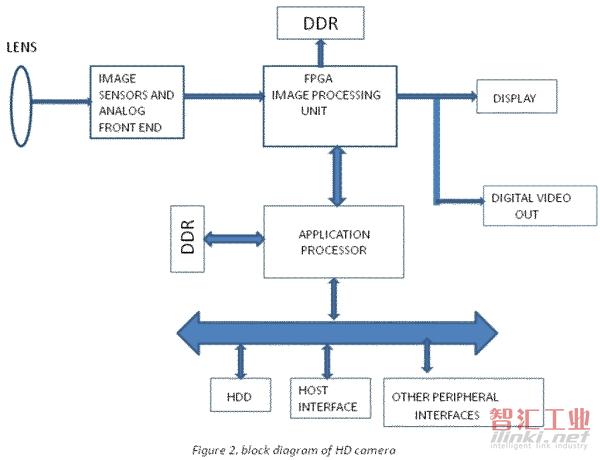

圖2顯示了一個用于電影制作和攝影棚的HD(高清)專業相機的系統框圖。捕獲到的圖像經過一個圖像處理器,進行色彩處理、亮度提高、數碼縮放、幀速率轉變等等。圖像處理單元通常使用一個基于FPGA的設計,由于大部分的圖像處理是專有的,會經常發生變化。應用處理器管理與其它設備的通訊以及壓縮并存儲捕獲到的內容到海量存儲(HDD)。應用處理器也有一個圖形引擎來進行屏幕顯示(OSD),它和進來的視頻混合后顯示。

從上述例子中,我們可以看到數據處理包括兩種類型:

1) 幀同步: 在一些任務中需要幀同步(例如,通過以太網傳輸和接收時,當碼流速度不斷變化而解碼器需要一個恒速的傳輸流)。雖然存儲器對同步的要求似乎很小,但當涉及到多個碼流時它可能很顯著。這種同步可以由一個異步FIFO實現。

2) 幀存儲: 幀存儲在這些地方需要:任何暫時的處理如幀率轉換,數碼變焦(縮放),或執行去隔行。儲存的幀數量隨著需要的臨時信息數目增加而增加。當視頻數據按照本來的順序時,幀緩存也必須是“先進先出”。

通過上面的討論,我們可以說,所有的儲存和同步都可以使用FIFO實現。那么理想的FIFO應該是多大的呢?一個典型的1080p 幀,10位 4:2:2格式將需要存儲器大小為39.55M位(每行像素數*每幀行數*每像素比特數= 1920*1080*20)。預計總容量可以通過需要存儲的幀數乘以這個數字。典型的視頻處理算法需要存儲2到3幀,這意味著總容量要達到120M位。由于不可能有如此大的基于片上SRAM的FIFO存儲器,一般的方法是使用一個DRAM來緩存這個數據。

高密度FIFO -傳統的實施和及其復雜性。

幀緩存就是高密度FIFO,傳統上使用外部DDR SDRAM實現。舉例說明一個典型的視頻處理應用和這些FIFO如何實現。

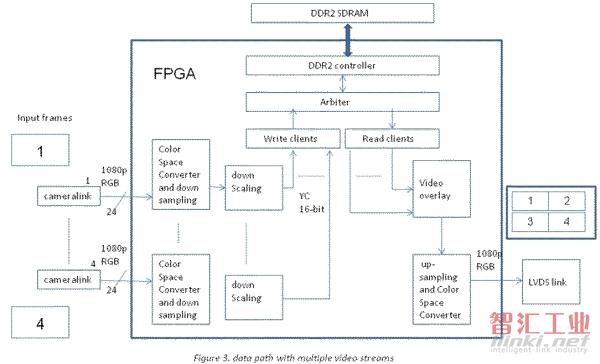

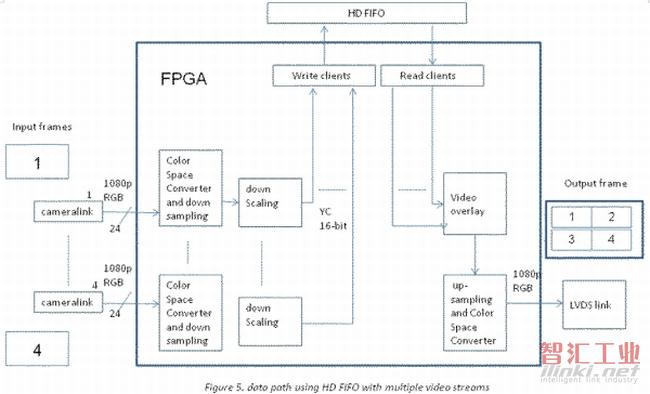

圖3顯示了一個典型情況的數據路徑,有4種不同來源的視頻流需要顯示在同一個顯示器上。四個以1080p60(24位RGB)分辨率捕捉視頻的高清相機使用一個cameralink接口連接到系統上。色彩空間轉換 (從RGB到YCbCr)及色度采樣降低(從4:4:4到4:2:2)后,橫向和縱向幀按比例減少,并儲存在DDR2 SDRAM里。存儲的幀可以按要求讀回和定位,結果幀和融合幀然后提高采樣速度和色彩空間轉換為通過LVDS連接來驅動面板。

讓我們看看存儲器大小和帶寬要求:

(i) 大小要求:

盡管這里沒有涉及到時間處理,為了避免一個源的兩幀被分開儲存,這樣當一幀正在寫時,另一個幀可能要讀回來。兩幀圖像的大小是((1920 * 1080 * 16)/ 4)* 2 ~ = 63.3M位。

(ii)帶寬要求:

由于讀和寫路徑為復用的,所需帶寬是讀、寫路徑帶寬之和。

寫路徑頻率=(每個客戶端頻率)*( 客戶端數量)=(148.5/4 )* 4 = 148.5MHz

讀路徑頻率=輸出幀分辨率頻率= 148.5MHz。

實際的工作頻率為( (讀頻率+寫頻率) / 2 +其它開銷),因為接口工作在雙數據速率,并且還有一些其它開銷,如DRAM存儲器刷新周期、bank地址切換等等。假設為80%的效率,那么將在185MHz的頻率運行。

(iii)內存接口大小和I / O需求:

當畫面以16位4:2:2格式存儲時,一個16位接口就足夠了。根據計算,FPGA 的I/O總數的為46:

時鐘引腳(2個用于差分時鐘,1個用于時鐘使能)= 3引腳

命令引腳(片選,RAS, CAS, WE)= 4引腳

地址引腳(14個地址線、3個 bank地址線)= 17引腳

數據線(X16接口)= 16引腳

數據選通及分離(4個引腳用于2微分DQS,2個用于分離數據)= 6引腳

高密度FIFO -離散的存儲器:

現在讓我們看看使用離散可編程高密度FIFO的實現方式和特性定義,這樣DDR2 SDRAM存儲器就可以由簡單的數據存儲便可以由簡單的數據存儲代替。

(i)多隊列特點:

如果FIFO存儲器定義為一個單一塊的內存,那么寫多個視頻流是不可能的。因此,FIFO必須能夠配置并分成多個隊列。在上文的例子中,有四種不同的畫面要寫,并且四個幀必須同時從不同的隊列同時。因此,我們的應用需要至少八個隊列。

(ii)分離和重傳:

有可能從一個標準的FIFO曾經讀過的數據又從FIFO丟失了。FIFO指針可以重新編程,允許任何幀都可以根據需求多次讀出。

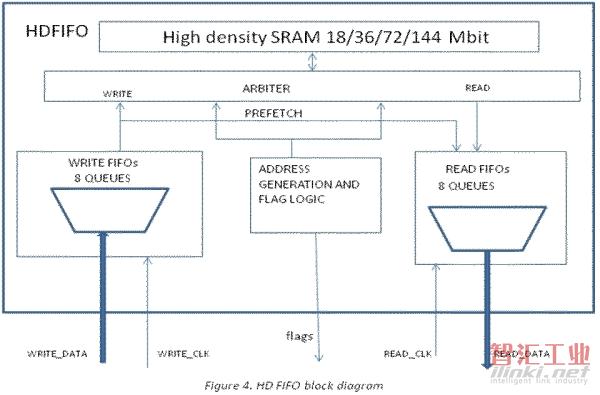

圖4顯示了賽普拉斯CYFX072VXXX HD-FIFO的框圖。

圖5給出了使用賽普拉斯HDFIFO替代DDR2芯片的應用案例。

讓我們再來看看存儲器大小和帶寬要求:

(i) 大小要求:

存儲器大小和DDR2 SDRAM的相同,為兩幀圖像的大小((1920 * 1080 * 16)/ 4)* 2 ~ = 63.3M位。

(ii)帶寬要求:

由于讀和寫路徑是分立的,讀、寫的工作頻率可以不同。這相對于DDR2 SDRAM來說有很大的優勢。

寫路徑頻率=(每個客戶端頻率)*( 客戶端數量)=(148.5/4 )* 4 = 148.5MHz

讀路徑頻率=輸出幀分辨率頻率= 148.5MHz。

實際的工作頻率對于讀和寫來說為單一的數據頻率148.5MHz,這里沒有額外的開銷,如DRAM存儲器刷新周期和bank地址切換。

(iii)內存接口大小和I / O需求:

當畫面以16位4:2:2格式存儲時,一個16位接口就足夠了。根據計算,FPGA 的I/O總數的為48:

時鐘引腳(1個用于寫時鐘,1個用于讀時鐘)= 2引腳

命令引腳(寫使能,讀使能,輸入使能,輸出使能,3個引腳用于選擇哪8個隊列寫,3個引腳用于選擇哪8個隊列讀,1個引腳用于分離,1個引腳用于傳輸)= 12引腳

數據引腳(16個引腳用于寫數據,16個引腳用于讀數據)= 32引腳

標志(1個引腳用于空標志,1個引腳用于滿標志)= 2引腳

離散HD-FIFO相對于傳統實現的優勢:

結構優點:

(i) 由于讀和寫路徑是分開的,沒有其它操作開銷,操作頻率可以降低一半以上,這些都是很顯著的優勢。

(ii)由于使用的是SDRAM控制器,不需要仲裁機制,FPGA內部邏輯變得更簡單。

(i) 信號開關頻率降低一半以上,允許增加建立時間余量,相對于DDR2來說沒有嚴格的輸出同步要求。

(iv) 設計里時鐘域的數量減少了,因此降低了相關時序切換和交叉時鐘域的問題。

電氣優點:

(i)減少了信號切換頻率,從而減少了線路板上的開關噪聲。

(ii) HD-FIFO 的IO邏輯可以是任何LVCMOS接口,相對于DDR2 SDRAM的SSTL2邏輯有更大的噪聲冗余。

節省成本:

在高端FPGA的解決方案中使用HD FIFO可以節省 FPGA資源,具體如下:

(i) SDRAM控制器,降低了所需的存儲器,I/O,和邏輯

(ii)視頻處理功能,這些功能可以采用多隊列特征在HD FIFO上實現,如:

a. 視頻信號的隔行/去隔行

b. PIP實施

c. 交叉信號處理

使用高密度FIFO可以節省邏輯元件,寄存器,內存和I / O,可以幫助開發人員把高端FPGA換為更小的FPGA,從而可以節省20 ~ 30%的成本。

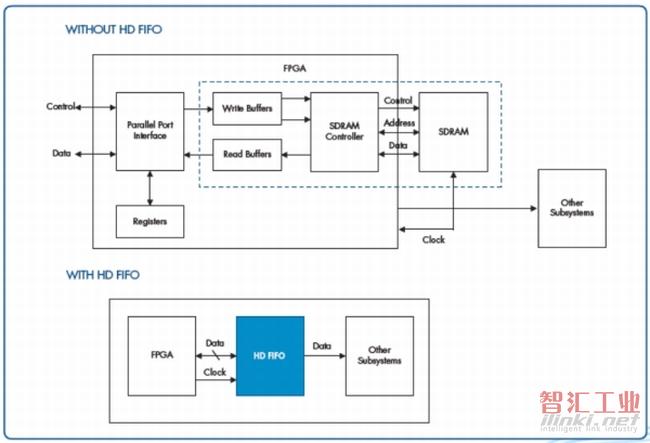

Figure6.有無高密度FIFO系統框圖比較。

高密度FIFO基于SRAM技術,為客戶提供了高數據可靠性和低延遲性。簡單易用的總線接口可以減少實施和調試工作。高密度FIFO密度可以達到144 Mb,速度可以到150 MHz,具備segment特色,還有很多增值功能,如多隊列和可選的存儲器架構,可以幫助開發人員設計更快、更有效率,從而使其適應廣泛的應用。它已經是一個成熟的解決方案,可以加速推向市場的時間,同時減少相關設計工作。該器件還可提供很寬的擴展選擇,可以適應視頻廣播,軍事,醫學影像,基站(網絡)設備,滿足很多應用,如:

普通高清格式幀緩存 (720p ,1080i ,1080p): 存儲四個1080p分辨率的幀

HDTV/SDTV幀同步

交換或格式轉換器盒子

高端數碼攝像機

軍事雷達中高密度緩存

醫學成像

基站--3G,4G及網絡

作者:Sivashankar M 和 Harsha Venkatesh

賽普拉斯半導體

(審核編輯: 智匯小新)

分享