1 引言

FIFO(First In First Out)是一種具有先進先出存儲功能的部件,在高速數字系統當中通常用作數據緩存。在高速數據采集、傳輸和實時顯示控制領域中,往往需要對大量數據進行快速存儲和讀取,而這種先進先出的結構特點很好地適應了這些要求,是傳統RAM無法達到的。

許多系統都需要大容量FIFO作為緩存,但是由于成本和容量限制,常采用多個FIFO芯片級聯擴展,這往往導致系統結構復雜,成本高。本文分別針對Hynix公司的兩款SRAM和DRAM器件,介紹了使用CPLD進行接口連接和編程控制,來構成低成本、大容量、高速度FIFO的方法。該方法具有通用性,可以方便地移植到與其他RAM器件相連的應用中去。

2 基于SRAM的設計與實現

2.1 SRAM結構芯片HY64UD16322A

靜態隨機存取存儲器SRAM(Static Random Access Memory)是一種非常重要的易失性存儲器,它的速度非常快,并且能在快速讀取和刷新時保持數據完整性。本系統SRAM器件采用Hynix公司的HY64UD16322A。HY64UD16322A是高速、超低功耗32Mbit SRAM,內部具有2097152個16 bit字容量。采用了CMOS制造工藝、TTL電平接口以及三態輸出,具有較大的輸入電壓和溫度范圍。同時HY64UD16322A支持DPD(Deep Power Down)模式,保證其在待機模式下功耗進一步降低。

2.2 系統硬件設計

整個系統采用CPLD作為控制核心器件。CPLD選用Altera公司的MAX7128AETC100-5。MAX7128基于Altera公司第二代MAX乘積項結構,是采用CMOS EEPROM技術制造的EPLD,它集成了2500個可用門,128個宏單元以及100個I/O引腳。

圖1是HY64UD16322A內部結構以及與CPLD接口設計的系統連接圖。可以看出,HY64UD16322A由地址譯碼、邏輯控制模塊以及大容量存儲陣列組成。CPLD接收到FIFO控制信號,按照該SRAM讀寫時序要求完成相應的讀寫操作,再通過所構造FIFO的數據輸入輸出和狀態控制接口返回。

2.3 指針算法程序設計

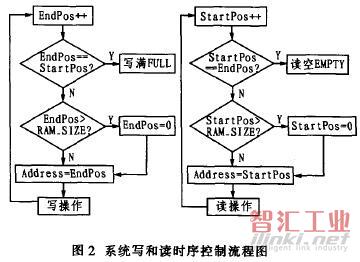

系統采用CPLD作為總控制器件。根據FIFO的特點,需要將SRAM按地址存儲用程序控制成先進先出的結構。這里采用指針算法來實現這種結構設計:設置兩個指針變量StartPos和EndPos,分別作為進入數據頭尾指針。當有新數據寫入時,數據從上一次存儲最后位置的下一個位置開始存放,存入一個數據,EndPos就自動加1,保持與最后數據位置同步。當EndPos超過整個RAM 的最大容量(RAM_SIZE)時,就需要循環返回,從0x000位置存放,一直到EndPos與StartPos重合,這時可以認為RAM 已經存滿。同理,讀出數據時,起始位置StartPos自動加1。當StartPos超過整個RAM 的最大容量時,就從0x000位置讀取,一直到StartPos與EndPos重合,這時可以認為RAM 已經讀空。在這兩個過程當中,CPLD需要對地址線進行控制。不難發現,寫數據的時候Address與EndPos一致。讀數據的時候Address與StartPos一致。圖2是整個系統寫和讀時序控制的流程圖。

2.4 時序控制

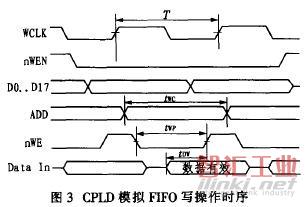

寫入數據的時候,CPLD需要模擬FIFO基本的寫操作時序:CPLD接收到nWEN(寫使能,低有效)和WCLK(寫時鐘,上升沿有效),即當nWEN為低,WCLK為上升沿時,將當前I/O上的數據寫入。在數據寫入RAM 的時候,CPLD應按照HY64UD16322A的寫時序來控制寫操作。這里,CPLD首先按照上述流程計算出當前數據應存放的地址,然后控制nWE信號,nWE為低時,數據自動寫入RAM。然后再寫下一位數據。整個寫時序如圖3所示。

同理,CPLD接收到nREN(讀使能,低有效)和RLCK (讀時鐘,上升沿有效)時,將最先寫入的數據讀出。這里,CPLD首先按照讀數據流程計算出當前讀出數據存放地址,然后控制nOE信號(低電平有效)。數據自動讀出RAM。然后再進行下一位數據讀出操作。

可以看出,影響所構建FIFO讀寫速度的關鍵因素是twc,該參數也是決定HY64UD16322A速度的主要因素,因此,所構建FIFO的理論速率應該接近HY64UD16322A的速率。

3 基于DRAM的設計與實現

3.1 DRAM 結構芯片HY57V281620E

一般來說,動態隨機存取存儲器DRAM(Dynamic Random Access Memory)是由大的矩形存儲單元陣列與用來對陣列讀和寫的支持性邏輯電路,以及維持存儲數據完整性的刷新電路組成。盡管操作較SRAM復雜,但由于DRAM具有每存儲位單元低成本和高密度的優點,使得它們成為商業領域最廣泛使用的半導體存儲器。本系統的DRAM芯片采用Hynix公司的134 217 728 bit同步DHY57V281620E。它由4塊2097 152x16 bit組成。采用了CMOS制造工藝。LVTTL電平接口。

3.2 系統硬件設計

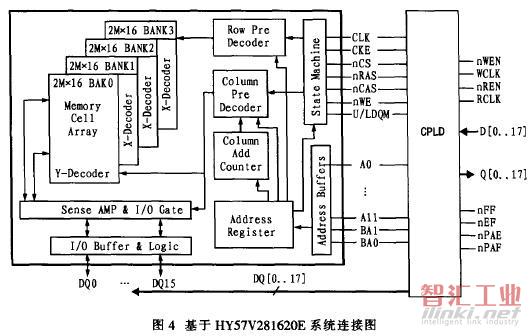

同樣采用MAX7128AETC100-5完成系統控制。圖4是HY57V281620E內部結構以及與CPLD接口的系統連接圖。接口控制原理類似2.2所述。不同的是.HY57V281620E內部由行列地址譯碼、多塊大容量存儲單元陣列和一些邏輯控制模塊組成。

3.3 程序設計

這里,主要采用2.3中設立頭尾兩個指針的思想。與SRAM不同的是。DRAM采用的矩形存儲單元陣列是由行線和列線來控制。并且內部采用分塊結構,這里HY57V281620E由4塊存儲單元組成,通過BA1和BA0來控制。在寫數據操作的時候。當存放數據長度超過當前存儲單元容量時。需要CPLD切換至下一存儲塊進行存儲,同樣,讀操作的時候也存在這種操作,即如果StartPos或者EndPos超過了存儲塊容量。這里是2097 152,則通過一個模4計數器控制切換至下一個存儲塊。

3.4 時序控制

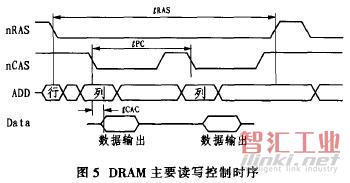

寫入(或讀出)數據的時候,CPLD需要模擬FIFO基本的寫(或讀)操作時序:CPLD接收到nWEN(nREN)和WCLK(RCLK),即當nWEN(nREN)為低,WCLK(RCLK)為上升沿時,將當前I/O上的數據寫入(讀出)。在數據寫入(讀出)RAM 的時候,CPLD應按照HY57V281620E器件的寫(讀)時序來控制寫(讀)操作:CPLD首先控制nRAS從高電平變至低電平,選擇行地址。再通過控制nCAS選擇列地址。這里,當寫入(或讀出)數據在同一塊當中進行,可以保持nRAS低電平,連續選擇多列數據操作(也稱作快頁模式讀寫)。當數據地址超過塊容量,則需要重新選擇行地址,然后再進行連續多列數據讀寫操作。讀寫使能控制和SRAM類似。通過nOE和BWE(低有效)來控制。

圖5是DRAM主要讀寫控制時序。可以看出,影響所構建FIFO讀寫速度的主要因素是tpc,這也是決定DRAM速率的關鍵所在。因此,所構建FIFO的理論速度也應該接近DRAM最高頻率。同時,還必須考慮DRAM 的刷新操作。這里,系統采用nCAS先于nRAS的方式(CBR),即控制nCS、nCAS、nRAS,并保持nWE為高電平,利用芯片內部計數器決定要被刷新的行。HY57V281620E提供了這種自刷新模式,刷新速率由tref來決定,通常為64 ms。在系統或某存儲塊長時間無操作的情況下,需要定時刷新。以保持數據完整。

4 實驗結果和分析

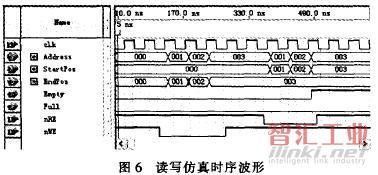

圖6是用QuartusII4.0根據2.3中設立的頭尾指針算法設計仿真出來的時序波形。

可以看出。系統從0x000底開始寫數據。當寫入3個數據時,EndPos增加到0x003。再進行3個數據讀操作,即StartPos增加到0x003,此時,所構建的FIFO是讀空狀態。可以看到讀空信號Empty在這時變為高電平。達到FIFO設計所需要求。

還需要注意:由于所采用的RAM 只采用一個數據總線作為輸入輸出,因此在寫數據的時候不能進行讀操作。而常用FIFO器件可以同時讀寫。所以,如果要在同一時間內進行讀和寫操作,那么需要在一個FIFO讀寫時鐘周期內對RAM 進行讀寫等多個操作,這時所構建的FIFO速率將降低。

此外,在與DRAM構建高速FIFO時,由于存儲塊選擇需要一定時間操作。因此跨塊存儲操作在頻率較高時會影響正常的數據讀寫,出現個別數據丟失情況。而且當某段時間進行刷新操作時,有突發數據需要讀或寫,這時不允許中斷。解決這種問題的辦法是用一個I/O引腳(nREADY)標識出當前所構建的FIFO是否可讀寫,如果有上述情況發生。則nREADY為高,可以讀寫時為低。

常用的FIFO器件還有半滿、接近滿、接近空等狀態指示,可以在上述構建FIFO的基礎上加上簡單的邏輯控制,計算StartPos和EndPos之間的差值,根據當前是寫操作還是讀操作來指示。其他狀態信號也可以通過CPLD經由邏輯運算很方便地實現。同時,讀和寫同步時鐘可以不一致,這樣就可以很方便地構成同步或者異步兩種FIFO,具有很好的可擴展性。

5 結束語

現在。SRAM的數據傳輸速率可以達到10 ns以內,DRAM要比SRAM稍慢一些。因此。SRAM通常用于高速緩沖存儲。而DRAM則通常用來存儲較大的數據。從成本來考慮,DRAM 比SRAM成本要低得多。

采用本文給出的結構和設計思想。避免了以往主CPU接管RAM時的一系列復雜讀寫操作。而直接類似FIFO使用,接口簡單方便,而且避開了傳統FIFO器件容量和成本的限制。本文通過理論分析,實際電路設計調試,已成功實現用兩種不同結構的RAM構建FIFO,并應用于多個實時高速信號采集系統中。

(審核編輯: 智匯胡妮)

分享