松下半導體(Panasonic Semiconductor)開發(fā)出了可將硅(Si)基板上形成的氮化鎵(GaN)功率晶體管的耐壓提高至5倍以上的技術。還有望實現(xiàn)3000V以上的耐壓。

硅基板上的GaN功率晶體管耐壓,本來應該是GaN膜耐壓和硅基板耐壓加之和,而實際上此前只取決于GaN膜的耐壓。因此,松下半導體為提高耐壓而采取了增加GaN膜厚度的措施。不過,多晶硅和GaN的晶格常數(shù)和熱脹系數(shù)不同,GaN膜過厚,就會出現(xiàn)開裂等問題。其結果,使GaN膜厚度從數(shù)μm左右、耐壓從1000V左右提高一直是難題。

對此,松下半導體解明了GaN功率晶體管的耐壓只取決于GaN膜耐壓的原因,并對該問題產(chǎn)生的原因——流過硅基板和GaN表面的泄漏電流進行了抑制,從而提高了GaN功率晶體管的耐壓。結果,使GaN膜厚度達到1.9μm,耐壓達到2200V,提高至原來的5倍以上。另外,松下半導體表示,如果使用過去曾報告過的9μm的GaN膜厚度,將有可能實現(xiàn)3940V的耐壓。

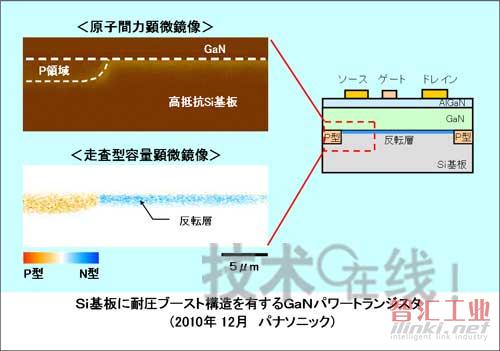

松下半導體的具體做法是,首先調查了由硅基板上的GaN決定耐壓的原理。結果發(fā)現(xiàn),在GaN晶體管的漏極加載正電壓時,硅基板和GaN表面會形成電子反轉層,導致出現(xiàn)泄漏電流,由于該泄漏電流的原因,會出現(xiàn)無法將硅基板耐壓計算在內的情況。接著,為了解決該問題,設計了在晶體管周邊部分的硅基板表面附近設置p型雜質層的耐壓升壓(Blocking Voltage Boosting,BVB)構造。通過在反轉層兩端設置p型雜質層,抑制了反轉層電子形成泄漏電流而流出的現(xiàn)象。最終可以將硅基板的耐壓計算在內,從而提高了耐壓。

另外,據(jù)松下半導體介紹,此次技術是日本新能源產(chǎn)業(yè)技術綜合開發(fā)機構(NEDO)共同研究業(yè)務的成果,已在2010 IEEE International Electron Devices Meeting(IEDM 2010)”2010年12月6~8日,美國舊金山)上公開。

(審核編輯: 智匯小新)

分享