前言

目前的ARM處理器已經適合應用于數控系統。ARM處理器的成本低而且種類多。主頻能夠滿足數控領域需求而且功耗比較低,無需使用風扇,提高了系統的可靠性。帶有MMU的ARM處理器支持數控軟件所需要的Linux操作系統,能夠充分利用現有的數控軟件資源。隨著ARM處理器和FPGA的快速發展,給數控系統的設計提供了新的解決方案。ARM處理器用作系統的核心,可編程FPGA器件作為運動控制器。同時 FPGA器件提供數控系統vo等其它輔助電路。

隨著PC/104成為工業控制領域的標準,已經被IEEE協會定義為IEEE-P996.1, PC/104總線提供的信號跟ISA總線一樣,但是前者的機械規格不僅易于擴充而且更加堅固,適合應用于數控系統。但是這種總線結構是在Intel的x86體系結構上發展而來,目前x86對PC/104的支持比較好,而ARM對PG/104的支持還不完全統一,主要由于ARM和x86在體系結構、總線時序、電氣特性以及指令集等方面的差異。而且不同的數控系統所需要的總線信號也不完全一樣。本文將提出一種基于ARM處理器的數控系統上支持PC/104總線的方案。

1 系統總體設計

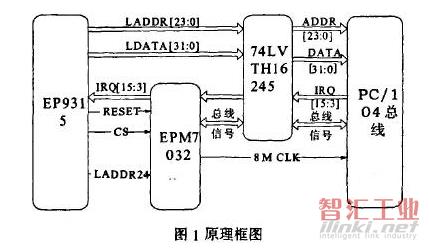

數控系統中的ARM處理器采用Cirrus Logi。的EP9315處理器,用EP9315的一個片選(nGCS3_PHBASE 0X30000000)作為PC104的地址范圍,用地址ADDR24來控制MEMORY和IO的方式的讀寫;用另一個片選(nGCSI PHBASEoxiooooo00)來查詢PC/104的中斷號,當Pcioa有中斷的時候,用一個中斷通知CPU,然后CPU通過nGCSI這個地址來讀中斷號,判斷出11個PC/104中斷源中來自哪個中斷。由于EP9315和CPLD在制作工藝、電氣性能上與PC/104總線有比較大的差別,因此需要使用74LVTH 16245作為3.3-5V電氣轉換buffer用來調整電平模式。CPLD是基于乘積項的可編程邏輯器件,CPLD內部采用固定長度線連接各個邏輯塊,因此具有較大的時間可預測性,引腳到引腳的延遲幾乎是固定的,與邏輯設計無關,因此適合作為PCJ104總線控制器。這里使用趕-to,的EPM7032用作PC/ 104總線控制器,用來完成EP9315讀寫時序向PC/104總線讀寫時序的轉換。EP9315的數據總線和地址總線連到電平轉換buffer,輸出到PCJ104總線上。因此PClioa總線設計的核心是保證EPM7032有正確的讀寫時序。原理圖如圖1所示:

2 PC/ 104總線控制器的實現

PC/104總線介紹

PC/104采用模塊化設計方法,通過自堆疊總線,省去了對底板或板卡插槽的要求。通過將多數信號的總線驅動電流減小至4mA,將元件數量和功耗降到最低。模塊的104個信號線分布在兩個總線連接器上,P1連接器有64個信號引腳,P2連接器有40個信號引腳。與ISA總線相比,PC/104總線將板卡的長寬比降至3.775英寸比3.550英寸(即9bmrn比90mm ),克服了ISA總線機械規格的缺點。PC/104總線與PC/AT總線兼容,也定義了兩種工作模式一8位和16位數據模式。對于8位數據模式,總線信號由板上的64引腳雙排插座Pl/J1提供,對于16位模式,增加了40引腳雙排插座P2JJ2。

ARM EP9315處理器介紹

EP9315處理器是Cirrus Logi。推出的一款基于ARM920T內核的R1SC處理器,主要面向工業計算機和手持設備等等。ARM920T是H award體系結構處理器,由ARM920TDMI、存儲管理單元(MMU)和高速緩存3部分組成。有獨立的16位指令cache和數據cache。ARM920T有5級流水線。EP9315工作頻率為200M Hz,集成了2D圖形加速器和協處理器,以及豐富的外設接口例如IDE控制器和PC MCIA控制器等,即使不使用額外的DSP芯片也能夠支持相當多的外設。EP9315支持LinxuMicrosoft lindawg CE等操作系統。

PC/104總線控制器的設計

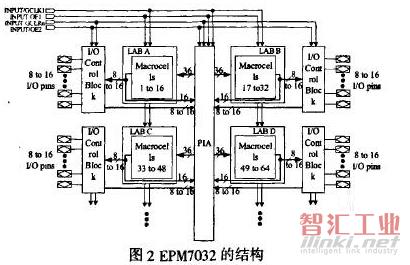

控制器的CPLD設計采用Altera公司的EPM7032,屬于MAX700()可編程器件系列。 MAX700()系列是高密度、高性能的CPLD,采用了Altera的第二代MAX架構,采用浮柵EEPROM設計。結構如圖2所示:

結構中包括邏輯陣列模塊(LA B)組成的陣列、可編程互連陣列(PIA)和可編程uo模塊陣列。每個LAB包括36個輸入端、16個輸出端和16個宏單元,每個宏單元包括處理組合和時序運算的組合邏輯和觸發器。PIA作為全局總線提供了多重LAB、專用輸入端和vo引腳之間的連接。PIA為邏輯單元的輸出和LAB的輸入提供了包括預計定時的完整連接。器件可以工作在3.3Y,pin-to-pin的延遲tPD=6ns,工作頻率可達151.5MHz,能夠與EP9315的AMBA總線時鐘頻率相匹配。EPM7032支持多種設計輸人,除原理圖外還可以通過VHDL, VerilogHDL和Altera Hardware Description language (AHDL)。VerilogHDL語言是一種硬件描述語言,能形式化地抽象描述電路的結構和行為,支持邏輯設計中層次與領域的描述,具有電路仿真與驗證機制以保證設計的正確性,用于算法級、門級和開關級的建模。開發環境使用Alters的MAX+Pluso

總線控制器的實現與仿真

在PC/104總線內部,用一個信號INTI查詢相關的中斷信號,使用片選信號CS3和地址信號LADDR24和讀寫信號wR.RD選擇MEM或者IO的讀寫方式。

3 Linux下的PC/104總線驅動程序的設計

在Linux中,由于有設備文件,所以才能使得用戶非常方便的訪問外部設備,Linux系統為外部設備提供一種標準接口,將外部設備視為一種特殊文件,可以像訪問文件一樣訪問一個外部設備。Linux通常將設備分為二種基本類型:字符設備、塊設備和網絡設備。在基于ARM處理器的數控系統中把PC/104總線看作塊設備。

4 結語

本文創新點:提出一種基于ARM EP9315處理器的數控系統上支持PC/104總線的方案,主要描述了ARM數控系統中的PC/104總線控制器的設計與實現,使用CPLD和Verilog HDL語言。實現了EP9315對PC/104總線讀寫信號的控制和中斷處理。完成了Linux下的PC/104總線控制器的驅動程序,提供了基于ARM處理器的數控系統的PC/104總線解決方法,彌補了ARM處理器對于PC/104總線的支持不足缺點,使得ARM處理器能夠更廣泛的應用于數控領域。

(審核編輯: 智匯胡妮)

分享